肖特基和离子注入碳化硅SIT

作者:海飞乐技术 时间:2018-06-04 17:59

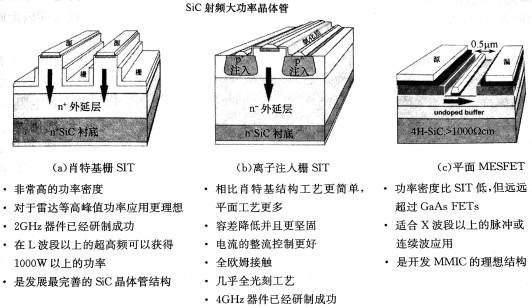

图1比较了制作在SiC上的肖特基势垒栅SIT、离子注入栅SIT,以及平面金属半导体场效应晶体管( Metal-Semiconductor FET, MESFET)。在肖特基势垒栅中,刻蚀出深沟形成沟道区,而且肖特基金属栅接触沿深沟侧壁在深沟底部形成。因此,肖特基势垒整流金属半导体结沿沟道侧壁形成,这与垂直MESFET结构相似。对于离子注入栅SIT,p+型栅沿源柱的两个侧面注入形成,这样就沿着沟道形成了pn结。由于p型栅形成了整流结,所以在p+型栅区只需要一个平面欧姆金属接触,这样就避免了沿着SiC沟道侧壁的淀积工艺。离子注入栅SIT和垂直结场效应晶体管( Junction FET,JFET)最相似。

由于在SiC中形成p掺杂区有一定难度,所以最早的碳化硅SIT采用肖特基势垒栅结构。在Si SIT中,虽然可以利用扩散工艺形成p+栅区,但是在SiC材料中非常困难,因为它需要非常高的扩散温度和非常低的掺杂物扩散率。因此,利用铝或硼离子注入到轻掺杂的沟道层形成p+栅是制造pn结SlT所需p+型区的最实际的方法(铝比硼更好,因为铝的激活能较高)。

随着能够控制离子注入到热SiC衬底上(高达1000℃)技术的出现和精确高温掩膜(退火保护层)工艺的发展,可以在激活离子注入掺杂物时保护SiC衬底,现在可以将离子注入栅SIT做在SiC上。离子注入形成的结对于大功率应用有许多优点,是实现高产量、高性能和稳定性微波功率晶体管的理想选择。离子注入栅在高达1750℃的温度中退火以修复SiC中的晶格损伤并电激活p型掺杂物,它们在高温和高电场条件下稳定可靠。离子注入栅SiC SIT能够阻止静电放电(高达16kV测试时,器件没有失效,也没有改变工作状态),而且不受电路上栅驱动电压的影响,与肖特基势垒栅SIT相比能降低表面拓扑(参见图1)。

通常,SiC上的离子注入栅SIT能改善以下性能:

(1)更高的工作电压,得益于有优良的边缘终端技术;

(2)由于统一的重掺杂n+源区(与栅区一样,利用离子注入形成),降低了源区电阻;

(3)因为更高的pn结内建电压,可以制作成常关态;

(4)器件工作时即使结温上升,pn结也很稳定;

(5)因为pn结的非破坏击穿特性,所以能防止静电放电;

(6)结击穿可逆(非破坏性);

(7)更好的抗辐照性能;

(8)采用平面离子注入器件工艺,成品率显著提高。

图形化注入时,离子注入在水平方向上的散射会钻蚀掩膜(也就是形成凸起),使栅-栅距离缩小,即不需要线宽更好的光刻就能得到比定义沟道宽度的掩膜尺寸略小的栅-栅间距。利用这种凸起形成更窄沟道的优点是:

(1)更窄的沟道宽度能提供更高的关断电压(更高的电压增益),而且优越的整流pn结能使电压增益最大;

(2)该凸起会使源区与栅区部分重叠,因此,在形成源区时不需要严格的对准精度;

(3)SiC芯片下方会出现很小的沟道宽度,这样,表面附近的沟道宽度比常规的栅结构大1~2µm,这就使沟道处的开态压降减小;利用离子注入栅结构,开态压降降低,是常规SIT结构的十分之一,而关断增益并没有减小;

(4)栅-栅间距和器件间距的减小,降低了寄生电容,增大了沟道电流、跨导和电压增益,这使器件工作于更高的频率。

此外,高的pn结内建电压(~3V,与SiC的能带宽度3.2eV成比例)有可能制造常关态微波功率晶体管,从而使其等效电路更简化。

上一篇:SiC欧姆接触的热稳定性

下一篇:PiN二极管的结构