碳化硅肖特基混频二极管

作者:海飞乐技术 时间:2018-03-27 11:26

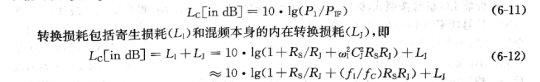

微波二极管混频器是将接收到的微波信号频率f1与本振(LO)信号通过混频器的非线性电阻进行混频,得到一个中频的差分信号fIF=f1-fLO,用以放大和检测信号。这种二极管通常利用金属-半导体接触的非线性电阻(RJ),因为它的少数载流子注入低,可以实现良好的性能,而不使用pn结。混频器的性能通过转换损耗(LC)决定,定义为

二极管混频器用于小功率微波信号变频,但它的本征转换损耗LJ随LO功率水平的增加而减小。事实上,目前的肖特基势垒正偏时可以通过热电子发射理论描述为

高性能LO信号按照式(6-18)和式(6-19)规律减少转换损耗LJ,提高混频器线性度,因为当输入信号功率与LO功率可以比拟时,转换损耗将增加。高性能二极管混频器的另一个优点是,当实现高成本LO功率时,交调失真减小。交调失真发生在频率f2的第二个信号到达RF端时,与希望的信号(f1)交互影响。二阶交调失真发生在频率fLO±(f1+f2),远离与理想的中频信号时,而且在宽带系统中更严重。由频率fLO-(2f1-f2)和fLO-(2f2-f1)交互产生的信号为三阶交调失真项,而且与理想中频信号非常接近。交调失真通常在信号与LO功率接近时产生,并且通常由输入功率截点决定(IIP2和IIP3分别为二阶和三阶交调失真项)——这里中频交调失真功率与有用信号功率相当。IIP越高,交调失真越小,无杂波动态范围越宽。

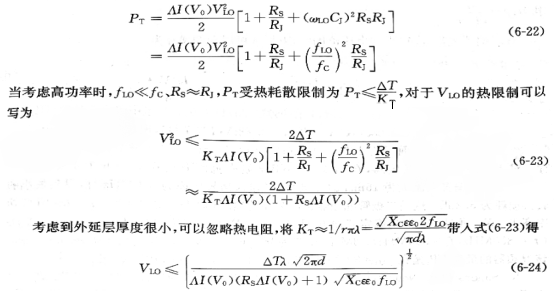

VLO值受热学和电学限制。忽略衬底和欧姆接触的电阻时,VLO受肖特基二极管在RJ=RS时最大正项偏压VMAX=V0+VLO的限制,即

VLO的热限制可以根据二极管总吸收功率(PT)推导。假设射频功率可以忽略,肖特基二极管吸收的LO功率与VA关系如下式所示:

表1 肖特基二极管混频器不同参数的品质因数(相对于Si的归一化值)

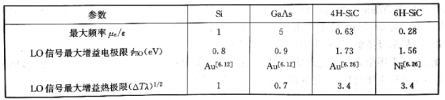

1997年,Fazi和Neudek首次提出用SIC肖特基二极管制造高级混频器。他们测量了中频输出范围在500 MHz的两个商用Si二极管输入单平衡混频器,碳化硅肖特基二极管与其相同,而且LO等级高20dB,频谱如图1所示。碳化硅SIC肖特基二极管混频器的转换损耗比Si二极管低2dB(12dB和10dB).SIC混频器中没有发现交调失真。由于SIC混频器至少比Si混频器低20dB的高噪声等级,使其不能精确确定IDM。

图1 信号平衡混频器的IF谱:(a)具有两个商用Si二极管;

(b)具有两个SIC二极管和20dB LO信号放大器

Eriksson等人已经发表了一系列关于Ti肖特基碳化硅混频器的制造及表征的文章。研究的二极管采用生长在高电导340µm厚4H-SIC衬底的Si表面。衬底施主浓度为1.1×1019cm-3。在4H-SIC衬底顶部生长重掺杂间隔层,接着生长厚度为0.38µm、施主浓度为3.1×1017cm-3的漂移区。台面结构通过Ar离子束刻蚀得到。肖特基势垒通过剥离技术的Ti-Au蒸镀形成。背面接触通过Ni蒸镀,并在950℃。Ar/He(10:1)气氛中退火5分钟形成。二极管的肖特基势垒高度ф=1.08eV(C-V测量),ф=0.88eV(I-V测量),理想因子低于1.10。

(b)具有两个SIC二极管和20dB LO信号放大器

图2 测量SIC肖特基势垒混频二极管的混频器

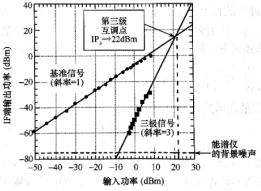

图2显示了接触面积为1.5×10-5cm-2(40×40µm2)的单平衡混频器的连接和特性。对于P LO=15dBm混频器,在0.2~1.4GHz频率范围时转换损耗低于10dB。对于PLO=25dBm、偏置电流lo为15mA的二极管,当输入信号频率为850MHz时,得到最小的转换损耗为5.2dB。这是二极管混频器转换损耗的典型值。该电路的最大外加LO功率高于1W。通过双色测试确定三阶互调节点。同等功率的RF输入信号被分10MHz(f1=850MHz,f2=860MHz)。IM和IF功率随RF功率变化的测量结果如图3所示。该混频器的最高IIP3是在fLO=800MHz、PLO=30dBm、lO=I5mA时的31dBm。

图3 SIC肖特基二极管混频器IF功率与IM功率随射频输入功率的变化,其中PLO=30dBm llP3,实线为测量结果,虚线为模拟结果

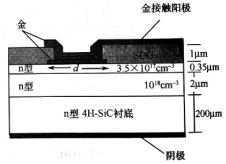

R.Simons和P.Neudeck报道了具有最高工作频率的SIC肖特基二极管混频器。二极管制作在n型4H-SIC衬底(Si面,0.036Ωcm)的同质外延层上,外延层的浓度和厚度如图4所示。将最初的晶圆从背面减薄到大约0.2mm。第一步:在晶圆的反面进行Ni金属处理,并在炉中高温退火形成阴极接触:;第二步:肖特基金属沉积(0.1µm厚的金),通过剥离工艺形成直径为5~50µm的阳极接触;第三步:通过多次旋涂玻璃形成厚度为1.0µm的绝缘层支撑大面积阳极接触引脚;第四步:光刻和干法刻蚀,将阳极上多余的SOG移除,形成圆形开口;第五步:采用金剥离工艺形成大的阳极接触引脚(100µm×100µm)。这一过程中,圆形开口也一起进行金属处理,以保证阳极和接触引脚的连接。

图4 SIC肖特基势垒混频二极管剖面结构

将直径为25µm的二极管接入到单平衡混频器电路中测试了线性特性。当输入功率从-40dBm到+13dBm时,转换损耗保持不变,大约为7.5dB。碳化硅肖特基二极管单平衡混频器如图5所示。从图中可以估算出无杂散动态范围近似为60dB,IIP3约为22dBm。上述测量中的转换损耗与商用Si肖特基二极管单平衡混频器相同。但是,得到相当的输入特性,Si肖特基二极管必须对双平衡混频器4个臂的两个二极管进行复杂设计。

图5 f1=1. 57542GHz, f2=1. 57842GHz, fLO=1. 55542GHz,PLO=19. 5dBm时IF端输出功率随输入功率的变化

上一篇:点接触二极管和肖特基二极管是什么关系?

下一篇:Si与SiC肖特基二极管应用对比优势