碳化硅二极管正向电压的退化

作者:海飞乐技术 时间:2018-05-07 20:55

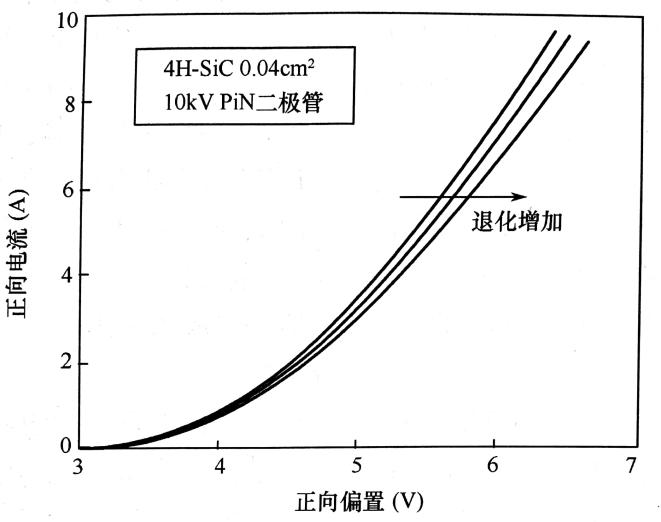

如果使用合适的边缘结终端和钝化技术,SiC器件的反向偏压工作将很稳定,在碳化硅 PIN二极管正向偏压工作时,发现了一个重要的现象,并且引起了对长时间工作的稳定性和可靠性问题的研究。根据观察,当pn结长时间处于正向偏压时,开态压降会随时间增加,如图1所示。这些器件显示正向偏压退化的持续时间从几毫秒到几个小时。PiN二极管开态压降(VF)的变化对于稳定性十分重要,因为这将导致电流熔化点和局部电流过大。如果一个二极管的一部分相比于其他区域有更低的导通电压,电流就会转移聚集到低VF区域。这将会导致器件的一小部分有过大的电流密度,而器件的其他部分电流密度很低,整个二极管热的分布不稳定,这种情况会使并联的器件变得不可靠。

图1 高压碳化硅 PIN二极管经不同正向偏置应力后的开态特性

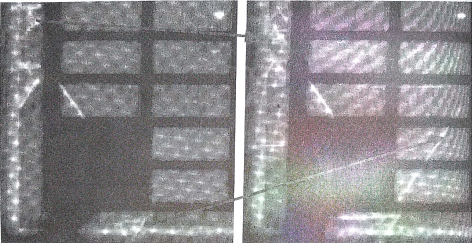

经历VF退化的PiN二极管的光学观察结果显示,这些二极管中具有材料缺陷形成的“伴生物”,如图2所示。对于这种称为“亮线缺陷”的现象最早由 Konstantinov在参考文献中报道,因为这些缺陷都是以移动的亮线形式出现。这种情况类似早先研究GaAs发光器件时,发现的“暗线缺陷”,这种情况就是由于非平衡载流子注入和晶格应变产生的位错生长,导致了相似的正向偏压退化现象。许多研究都一致表明,移动且扩散的晶格层错缺陷是PiN二极管正向偏压退化的主要原因。这个缺陷将会扩散到整个n-基区。最初认为,VF的增加是由于层错形成的复合中心导致的载流子寿命减少。但是,现在很多研究结果表明,VF的增加导致了层错的形成,这引起了电流流动的势垒并减小了传导区面积。在单晶SiC的原子堆垛顺序中,堆垛层错是二维缺陷。

图2 PiN二极管经正向偏置应力前(左图)后(右图)的发光測量表明层错在增长

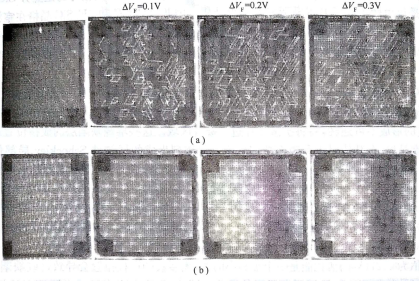

图3显示了同一个芯片上两个相邻的0.0152二极管,不同间隔下一系列退化的光发射图像。这些光学现象与载流子寿命的测试方法有关,测试的方法应用了高di/dt和低di/dt情况时的关断反向恢复波形。这个结果说明有效本征区载流子寿命没有减少,而VF的退化是由于电路导通面积的减小造成的。图4(a)和(b)显示了同一个二极管的正向压降退化和反向恢复电流(图2和3显示的)。图4(a)和(b)中的箭头标明了时间。图3(a)中的菱形区域说明了层错源于表面,大概源于pn结。因为最高的过剩载流子浓度位于pn结附近,所以图4(a)中的器件迅速退化。图3(b)标出的黑色三角形区域说明了n+/n-结附近生长的层错。白线部分表明没有位错,黑色区域说明了电流减小。图4(b)显示,器件的退化在开始时很慢,这是因为层错靠近本征区的底部,而这个区域的过剩载流子浓度很低,然后由于过剩载流子浓度相对较高的表面上层错接近pn结,退化速度增加。

图3 同一芯片上(a)上面和(b)下面两个相邻的二极管在不同间隔下退化的光发射图像

图4 与图3同样整流器的正向压降退化(100A/cm2下的VF)(a)和反向恢复电流(b)

对于这些位错的基本特性、来源和传播方式,许多研究者进行了广泛的研究,现在已经确定这些位错源于衬底六角形SiC(如4H和6H)晶格缺陷。当三个不同的原子面以特殊的顺序进行堆叠时,形成了SiC多晶六角形晶格结构。与其相对的是立方SiC(3C),立方SiC是仅由两个原子B堆叠形成的二维结构。因此,4H-SiC和6H-SiC晶格在室温处于亚稳态,如果有一个合适的成核位置,就可以转变成类似3C结构的局部缺陷。这种情况的出现需要一定种类和浓度的成核位置,也需要以电子-空穴对复合形式存在的活化能。控制这些缺陷的来源和扩散,在于控制形成这些缺陷成核位置的已有缺陷。

相对于非退化pn二极管在禁带附近形成的紫光光谱,电致发光的光谱分析显示,这些亮线代表的缺陷发光为红光和近红外线光谱区域。这些缺陷是与晶格位错相关的线性缺陷网络,它的形成不可逆转,并将扩散并穿过二极管区域。这些堆叠缺陷层的成核位置最先出现在小角度晶界,在其他衬底和表面缺陷之中。观测到生成的层错被Shockley局部位错所限制,其中伯格斯矢量为b=1/3<10`10>。这表明缺陷通过三角形或者菱形结构进行扩散,其边界沿(11 `20)方向。当二极管保持在正向偏压状态时,这些循环结构增加而且扩散。光谱测试说明层错的发射光谱范围为(450士20)nm,而且贯穿的位错在(700士20)nm范围。计算所得局部位错的扩散活化能在(0.27士0.02)eV范围。实验中,这些缺陷的扩散速度为7×10-5m/s。

数值为0.27eV的活化能是够小的值,大多数的成核位置会导致这些缺陷的形成,而且会导致某些PiN二极管开态压降的退化。因此,解决方案在于减小器件有效部分的缺陷。一个新的解决方法就是生长没有微管缺陷的Lely晶体,只在衬底顶部有极少的缺陷。实验中发现,使用常规衬底的pn结整流器件时,200A/cm2的正向电流并没有引起器件任何的性能退化。现在,4H-SiC外延生长技术已经有了长足的进步,通过减少材料缺陷密度可以生产无漂移PiN结构。初步的研究结果表明,材料缺陷的减少直接与获得高成品率的无漂移SIC PIN二极管相关。

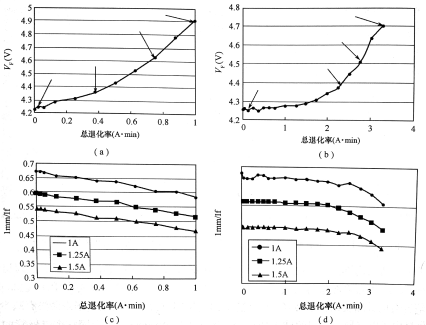

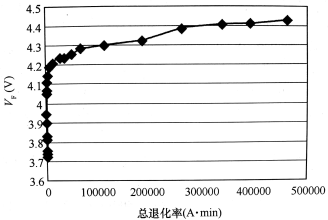

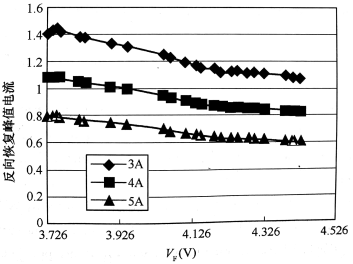

现在,有很多种方法可以改进VF的退化。不同方法产生无退化器件的成品率不同,有些方法的无退化成品率可以达到86%。各种无退化的工艺过程,有些可以使器件没有任何漂移,少数只有很小的漂移并且很快就趋于稳定。但是,有些工艺过程却降低了击穿电压的成品率。最近,一种新的低基面位错(BPD工艺显示了其在所有方面都有明显提高,击穿和漂移的成品率分别为35%和70%。图5和6显示了50A 10kV 4H-SiC PIN二极管的典型的低退化率。

图5 50A应力下0.5cm2 10kV 4H-SIC PIN二极管导通压降VF(50A/cm2)随总退化率的变化

图6 0.5cm2 10kV 4H-SIC PIN二极管反向恢复峰值电流随总退化率的变化

值得注意的是,即使功率密度(正向电流乘以VF)达到与pn结二极管接近的水平,也没有在肖特基二极管单极器件中观察到这样的现象。数据显示,与层错相关的正向偏压退化出现在双极SiC器件,如晶闸管、GTO、PiN二极管和双极结晶体管(BJT)中,然而对于单极开关器件,如MOSFET和JFET,并没有发现类似的情况。这些位错的扩散随电流密度增加。更高的温度和更厚的外延层也会导致更高的位错形成率。探针刮痕、芯片切割线和pn结二极管上的硅化物接触都被认为是位错迁移和扩散的成核点。

上一篇:碳化硅二极管成品率限制因素

下一篇:功率快恢复二极管反偏ESD机理分析