功率快恢复二极管反偏ESD机理分析

快恢复二极管(fast recovery diode,FRD)是一种应用广泛的功率器件,其可靠性对整个电路甚至系统的正常工作至关重要。静电放电(electrostatic discharge,ESD)电压高,瞬时电流大,会对整个电路甚至系统造成极大的危害,可能产生严重后果。一些高端应用会对其ESD指标提出较高要求。虽然在集成电路领域,低压ESD保护器件的研究与开发已相当成熟,但高压FRD的结构参数及发生ESD的情况与其不尽相同,需专门进行针对性研究。目前,国内外公开发表的关于功率FRD的ESD机理研究文献较少。作为这方面工作的一次尝试,本文首次采用一种简化的分段线性电流源模型,利用半导体器件仿真工具对FRD在反偏ESD测试中内部状态的演化过程进行了展示和分析,并在此基础上讨论了器件结构参数对FRD抗ESD能力的影响。

1. ESD测试的仿真模型

ESD测试中经常采用人体模型(human body model,HBM),但器件仿真(实际是器件与电路的混合仿真)中若采用实际的ESD测试电路,就需要设置和调整电容、电感、开关、信号源等元件以模拟电路中的瞬时变化,并需要添加一些辅助信号源以模拟分布参数对这个瞬时变化的响应,加上热电耦合计算,很容易造成占用资源多、耗时长、收敛困难,而仿真波形却仍不理想的局面。为使问题得到简化,尽快获得对器件设计有指导意义的结论,本文尝试采用一种符合GB/T 17626.2标准的分段线性电流源模型,用以模拟FRD反偏下所受到的ESD冲击情况,并将该电流源直接作用到FRD上而不添加任何其他的电路元件,由此展开简单快速的仿真计算。

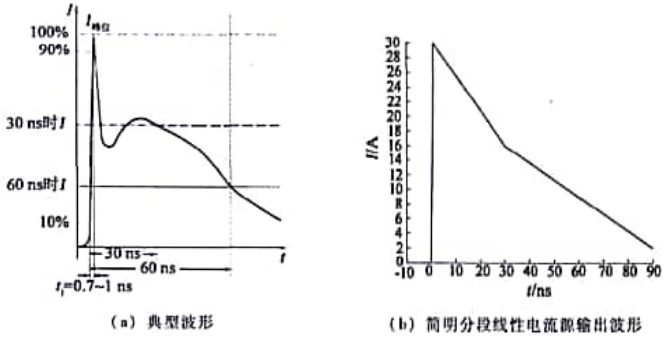

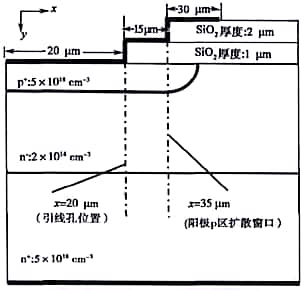

HBM静电放电发生器输出的典型冲击电流波形如图1(a)所示,参考图1(a)的波形参数所设计的8 kV简明分段线性电流源,对应波形如图1(b)所示。其中,0~1 ns内,电流由0 A线性上升至30 A;1~30 ns内电流线性下降至16 A;30~91 ns电流线性下降至1 A。由于该电流源电流下降速度比标准波形更缓,大电流持续时间更长,所以理论上对器件的冲击会比典型波形更严重。FRD的ESD过程仿真采用ISE软件,所用物理模型包括:与浓度、温度、电场相关的载流子迁移率模型、SRH复合模型、Auger复合模型、禁带变窄模型以及适用于高温的Unibo碰撞电离模型。同时,引入了热电耦合方程。作为一个研究起点,选取了一个只包含主结及其场板的简单二极管结构作为参考结构,其结构参数见图2 。计算中设定了面积因子,使有源区面积达到1mm2,仿真得到的静态击穿电压约为375 V。

2. FRD反偏ESD过程分析

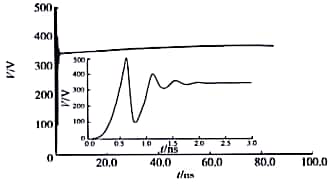

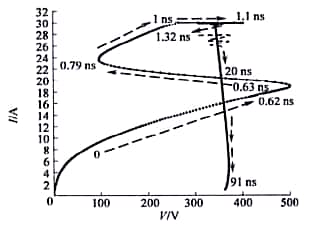

参考二极管在如图1(b)所示的反偏ESD冲击下所形成的电压波形仿真结果如图3所示,插图为0~3 ns电压放大波形。可以明显看到,在ESD冲击下,器件电压经历了过冲、负阻和振荡以及平缓发展3个阶段。其中,电压过冲发生在0.62 ns,形成的电压峰值高达500 V,明显超过此后的电压值,同时也远大于器件的静态击穿电压(约375 V)。随后,在电流继续急剧上升的同时,大约在0.8 ns,电压波形迅速下跌至略低于100 V,形成了瞬时的微分负阻现象,并由此开始了一个振幅迅速衰减的电压振荡过程。大约在3 ns之后,振荡消失,器件进入平缓发展阶段,电压保持相对稳定,在350~370 V内缓慢上升。图4给出了该过程伏安变化的轨迹。

为进一步探究上述外端特性演化所对应的内在机理,在图2中的x=35µm截线处,即pn结的拐角附近,提取了不同时刻器件的内部数据。下文将对此进行简要分析。

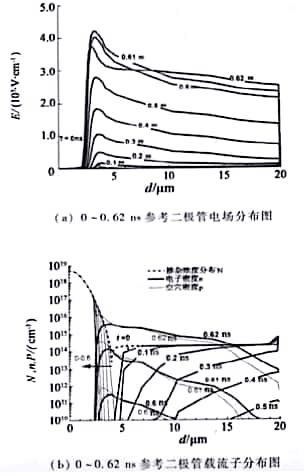

2.1电压过冲阶段

由上述ESD电流源模型可知,0~0.62 ns内反向电流处于迅速上升的阶段。在器件内部,这首先是通过pn结承受反压,势垒电容充电形成位移电流来实现的。此阶段x=35µm截线处电场及载流子分布分别如图5(a)和(b)所示,d为层面距离,E为电场强度。可以看到,在0~0.62 ns,pn结两侧的电场逐渐增强。一开始是呈三角形分布。至0.3ns,n-区电子浓度明显低于背景掺杂,表明n-区全部耗尽,同时n+区对电场有截断作用,电场开始呈梯形分布,且继续增强,外部电流由p+区空穴和n+区电子提供。至0.5和0.6ns,pn结处和n-n+结处的电场依次超过2.4×105V/cm,接近或达到临界击穿场强。此时,n-n+结也开始发生雪崩倍增,并将构成外电流的另一个重要来源(如前所述,势垒电容位移电流是第一个来源)。但是,由于相应的碰撞电离产生率是有限的,在0.1 ns级的短暂的时间内,尚不能产生出足够多的载流子(图5(b));同时,外部电流仍然迅速增加。因此,直至0.62 ns之前(如0.61 ns),电流仍然主要由p+区和n+区的继续耗尽来维持。于是,电场强度和器件所承受的反压在这段时间内不会因雪崩而钳位,而是持续增加,这就形成了外部的电压过冲和内部的“过耗尽”。由图5(a)可见,电场峰值在0.61ns时达到最大,高达4.2×105V/cm;耗尽区在0.62 ns时向p区一侧的扩展由于“过耗尽”而达到最大。

2.2 负阻振荡阶段

0.62 ns实际是电压过冲与负阻振荡的分界时刻。由图5(b)可见,在该时刻,pn结处的雪崩倍增实际已使载流子大量增加,大部分n-区的载流子浓度已超过背景掺杂,形成了显著的雪崩注入和电导调制。随着时间的推移,如图6(b)所示,至0.65和0.7 ns,雪崩注入的载流子浓度达到最大,E为电场强度。这些载流子开始对外电流的维持做出贡献。同时,考虑到载流子漂移速度此时因电场强度超过1×105V/cm而达到了速度饱和vd,sat,因而电流密度必须靠足够大的载流子浓度来维持。例如,对于空穴而言,为了维持一个电流密度j,其空穴浓度需要达到p=j/qvd,sat。此时,当j超过一个临界值jcrit(jcrit=NDqvd,sat)时,则p>ND。式中,ND为n-区掺杂浓度。

这种情况下,pn结附近n-区一侧原有的空间电荷密度ND将增加至p+ND(pn结附近n<<p,可忽略)。根据泊松方程,此处电场下降的斜率将增大。当p>>ND时(如0.62 ns以后)则电场下降率将取决于p,并急剧增加。同理,在n-n+结附近,电场也因大量电子的存在而发生类似变化,最终呈“U”型分布。

这种电场分布的改变,缩小了所包围的面积,所以相应外加电压将迅速减小,这就形成了瞬时的微分负阻效应。至0.8 ns,电场所包围的面积达到最小,外加反压降至100 V以下。

之后,电压波形开始振荡,其内在的原因是漂移速度趋于饱和(强化了载流子浓度与电流密度的关联)、载流子的雪崩注入(尤其是过耗尽阶段所造成的过电场及相应的过量雪崩注入)以及过剩载流子被清除等因素之间的相互作用。

由图6和图7可见,在0.65~5ns,载流子浓度和电场强度分别出现两次反复的涨落。这些变化与电压在相应时段的振荡是相符的。

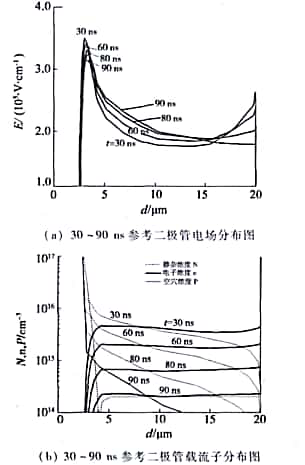

2.3 平缓发展阶段

图7和图8表明,n-区载流子浓度和电场强度在5ns以后基本呈单调且缓慢的变化。随电流的减小,载流子浓度开始下降,这就使得pn结和n-n+结附近的空间电荷密度下降,电场下降变缓,U型电场分布所包围的面积有所增加,所以相应的外压变高,器件实际仍处于微分负阻区。至90 ns,电流下降为1 A,电场开始由U型分布向梯形分布转变,器件再次回到微分正阻区(参见图3)。

2.4 讨论

如前所述,本文的仿真计算忽略了实际电路中的寄生参数和分布参数,但仍然明确得到了电压过冲和振荡的结果。这表明,考察实际ESD测试中波形振荡的成因时,既要充分考虑线路中的分布参数,也决不能忽视器件的固有特性。本文采用简单电流源模型所做的分析,实际正是针对后者进行的,所得的结果可认为是器件的“本征”ESD过程。实际测试中发生的振荡会更加激烈,持续的时间更长,但总趋势与本文是一致的。

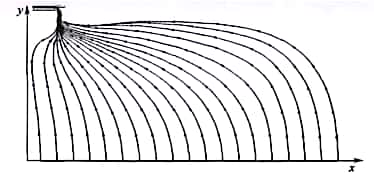

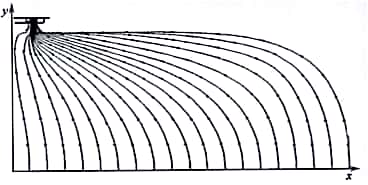

此外,前述的反偏ESD过程中载流子密度与电场强度的演化,涉及到了强场下的碰撞电离和雪崩注入。显然,这些情况会优先在电场最强的位置发生,而且由于负阻效应的存在,这个过程一旦发生,电流就会集中在这个位置。对于本文给出的参考二极管结构而言,这个位置就是pn结的拐角处,即x=35µm附近。

图9给出了0.63 ns时刻的电流线分布,直观地表现出二维结构中的这种电流集中。电流集中加大了局部的电流密度,使得在外电流的表观密度远小于由式(1)给出的临界电流密度时,就可以发生负阻效应。事实上,这种由电场增强和集中引起局部电流集中,进而在高电流密度下出现负阻效应,引起电场U型再分布的现象,与L.Egawa的二极管静态二次击穿分析和M.Domei的二极管动态雪崩分析是一致和相通的。可以认为是一种动态二次击穿。

二维结构中电流的集中还只是相当于一个垂直于纸面的电流带,在真实的三维器件结构中,电流集中实际会演变为电流丝。电流丝的形成会引发局部温度出现迅猛的上升,极端情况下会在几十纳秒内烧毁器件,这与动态雪崩问题是类似的。本文中参考二极管二维结构的热仿真并未得到很大的温升。通过大大增加有源区宽度(计算量亦大增),可使电流集中趋近于三维情况下的电流丝。后续的改进工作正在进行中。

3. FRD结构参数对抗ESD冲击的影响

研究FRD反偏ESD冲击的最终目的是为了寻求提高器件抗ESD能力的方法。为此在参考二极管的基础上改变相关结构参数,以考察不同结构参数对抗ESD能力的影响。

n-区的掺杂浓度和厚度决定了二极管的耐压等级,当参考二极管n-层的掺杂浓度提高到2×1015cm-3时,10ns时刻n-n+结处的电流密度峰值与相应的参考二极管相比下降了62.5%,电场亦减弱。由式(1)可知,n-区掺杂浓度高,对应负阻临界电流密度就增大,使电流集中较不易发生。因此,低压二极管的抗ESD能力比高压二极管强。

为加快二极管的反向恢复过程,往往采用减小阳极注入效率,即降低表面掺杂浓度来实现。但仿真发现,若将参考二极管阳极浓度降低到1×1016cm-3,则10 ns时刻n-n+结处的电流密值上升了31.7%。仿真计算表明,在器件引线孔边缘处,即x=20µm附近(见图3),由于在反偏ESD最初的过耗尽阶段,耗尽区已穿通整个p区,到达表面电极,从而在引线孔边缘处形成了急剧的电场增强,并引起电流集中,如图10所示。可见,低表面浓度器件对抗ESD可能是不利的。

另外,FRD中常用的n型缓冲层结构,对抗ESD能力也是有利的。仿真发现,在10ns时刻,带有缓冲层的结构在n-n+结处的电流密度峰值比参考二极管下降了70%。

由于简单的参考二极管结构与实际二极管的结构不尽相同,同时本文的“本征”二维仿真与三维结构和实际电路亦有差距,所以上述结果与实际情况并不能精确一致,但其反映出来的总趋势与实际生产中的经验是一致的,即:高n-区浓度(低耐压)、高阳极表面浓度及缓冲层结构有利于器件抗ESD能力的提高。由此可见,本文的仿真是合理有效的和具有指导意义的。

4. 结论

采用简明分段线性电流源,对参考二极管结构的本征反偏ESD过程进行了仿真分析。结果表明,其端电压波形的变化经历了电压过冲、负阻和振荡以及平缓发展3个阶段。相应地,器件内部则经历了过耗尽、雪崩注入、电场分布U型化、载流子及电场分布涨落等复杂变化,并在pn结拐角处造成局部电流集中。在此基础上,计算了器件结构参数变化对抗ESD能力的影响,所得结论与实际的生产经验是一致的。这也验证了本文仿真分析的合理性和有效性。

上一篇:碳化硅二极管正向电压的退化

下一篇:CAL技术在现代快恢复二极管中的应用